使用SIMULIA真瞬态 EM/电路协同仿真来设计可靠的背板

日期:2025-06-04 发布者: SIMULIA 浏览次数:次

在这篇博文中,我想展示如何使用 SIMULIA 真瞬态 EM/电路协同仿真来设计可靠的背板。我将展示如何在仿真中计算 KPI 和品质因数(如眼图),而无需测试物理原型,并演示瞬态协同仿真 (tran-co) 相对于宏模型电路仿真方法的优势。

使用 IBIS-AMI 进行背板建模简介

长距离背板的设计是一项具有挑战性的任务。通常,数据速率高达数十 gigaud,通道长度约为 1 米。损耗角正切 = 0.02 的 FR4 等传统电介质将导致如此长的通道上出现明显的插入损耗 (IL)。需要具有较低损耗的新材料来减轻 IL。发射器、接收器和连接器的线路阻抗应匹配以实现低回波损耗 (RL)。

输入/输出缓冲器信息规范 (IBIS) [1] 在业界被广泛接受,用于输入/输出 (I/O) 缓冲器的建模。IBIS 算法建模接口 (IBIS-AMI) [1] 允许供应商特定的均衡和时钟恢复算法,这是串行器/解串器 (SerDes) PHY 的强制性部分。AMI 仿真的第一步是获得无源通道和 I/O 缓冲器模型的脉冲响应,它等于阶跃响应的导数。

真正的瞬态 EM/电路协同仿真

在传统工作流程中,首先计算无源通道的散射参数(S 参数),然后通过标准宏建模转换为 SPICE 模型。最后,通过仿真 SPICE 模型获得阶跃响应。

与传统工作流程相比,引入了一种新的瞬态电磁/电路协同仿真 (tran-co) 方法 [2] 来计算阶跃响应,而无需使用 S 参数和宏模型,该方法在时域中同时求解麦克斯韦方程组和电路单元(例如 IBIS 模型或交流耦合电容器)。事实证明,它比传统工作流程更快,并且还可以避免非物理行为。

背板无源通道上的插入损耗

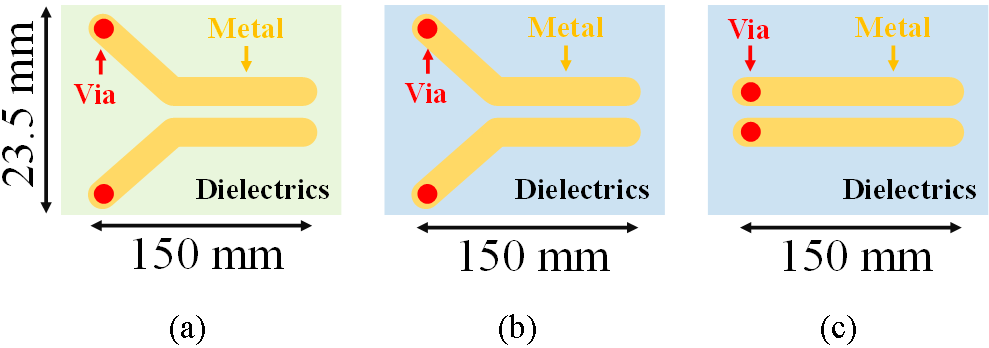

在设计 1 米长的无源通道之前,需要研究三个较短的测试板。测试板 A:损耗角正切 = 0.02、介电常数 = 4.2 且阻抗不匹配的电介质;测试板 B:损耗角正切 = 0.008 且介电常数 = 3.2 且阻抗不匹配的电介质;测试板 C:磁介质,损耗角正切 = 0.008,介电常数 = 3.2,发射器和接收器的匹配差分阻抗为 100 欧姆。

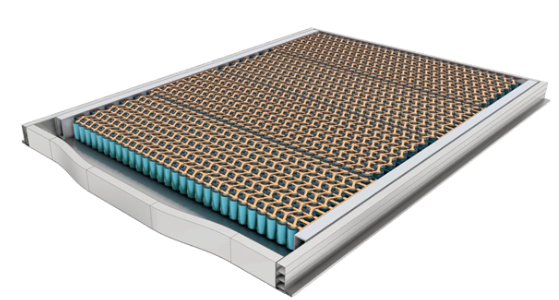

图 1.三个测试板 A、B 和 C,尺寸与金属材料相同,铜相同。

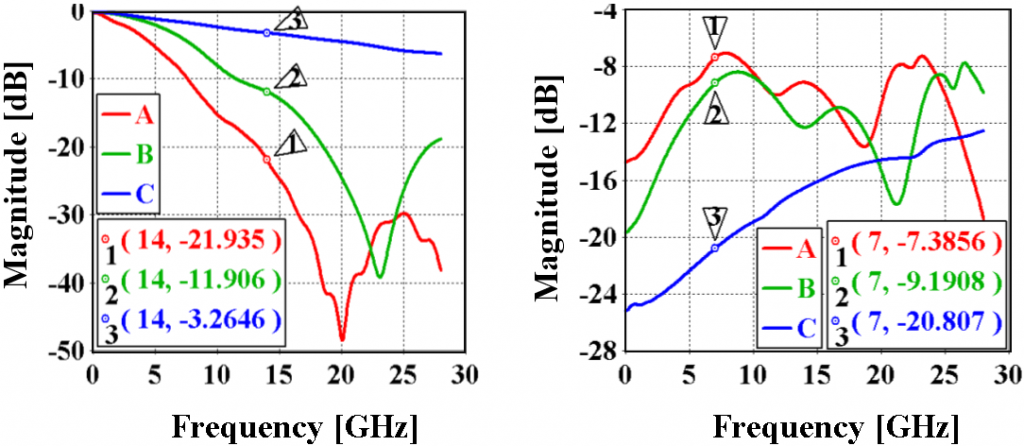

仿真结果总结如下图。通过比较下图左图中曲线 A 和 B 的 SDD21,我们可以观察到介电损耗对插入损耗的影响。对于 1 米长的通道,损耗角正切 = 0.02 的典型电介质(如 FR4)将导致显著的插入损耗,对于 150 mm 通道,插入损耗已经下降到 -12 dB。因此,首选损耗较低的新材料。比较右图 B 和 C 的 SDD11 曲线表明,保持阻抗匹配很重要,尤其是在过孔和连接器处,因为差分对的横截面可能会发生显著变化。

图 2.测试板 A、B 和 C 的仿真结果(左:SDD21,右:SDD11)

SerDes 阶跃响应的宏模型

在下文中,我们计算 SerDes 通道的阶跃响应,其中包含 IBIS Tx/Rx 缓冲器模型、交流耦合电容器和 3D 无源通道。

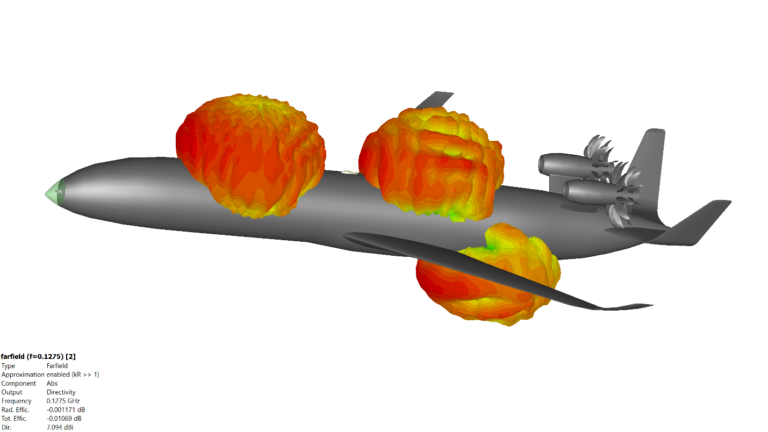

图 3.整个仿真网络包括 3D 模型和电路元件。

首先计算 3D 无源通道的 S 参数,然后将其转换为宏模型,该宏模型可以与电路元件(即 IBIS 模型和交流耦合电容器)一起在时域中进行仿真,以获得阶跃响应。在本博客中,此工作流程称为传统工作流程或电路工作流程。然而,对于长无源通道(例如数十 λ,自由空间波长为最大仿真频率 λ),S 参数计算可能非常耗时,并且标准的宏建模过程可能会导致系统级仿真效率低下(由于最终电路的尺寸较大)和精度下降(由于传播延迟建模不准确)。为此,我们引入了 tran-co 工作流程 [2],它不需要计算 S 参数或宏模型,而是在时域中一起逐步求解 3D 无源通道和电路元件以获得阶跃响应。我们将 circuit 和 tran-co 工作流程应用于测试板 C,并在下表中总结了它们的性能。

表 I..测试板 C 的仿真统计

最大频率。 板长 网格单元 电路 Tran-co

112 千兆赫 150 mm ≈ 56 λ 68,186,250 117 分钟 86 分钟

如上表所示,tran-co 工作流程比 circuit 工作流程更快。模拟在 CPU @2.0 GHz、GPU 2xKepler Tesla K40c+m 和 256 GB RAM 的机器上运行。

比较瞬态协同仿真和宏观模型电路仿真

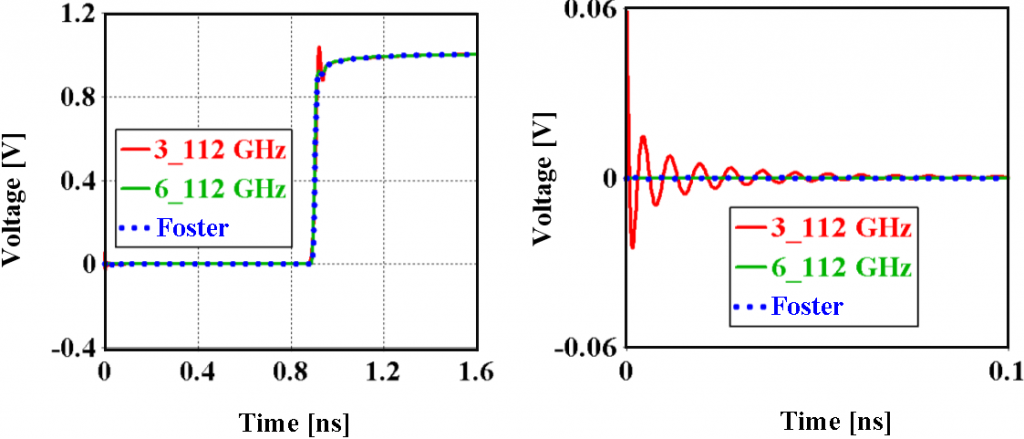

将 tran-co 工作流程的阶跃响应与通过在电路求解器 [3] 中使用残基极形式 (Foster Pole-Residue [2])仿真宏模型合成而获得的结果进行了比较。如下所示,当使用合成为集总元件的宏模型时,非物理纹波出现在阶跃响应的开头(红色,3_112 GHz)。但是 tran-co 工作流程(绿色,6_112 GHz)和电路工作流程中基于极点/残数的宏模型(蓝色,Foster)的结果相互匹配,可以避免非物理行为。

图 4.阶跃响应 (a) 与 t = 0 周围的放大视图 (b) 的比较。

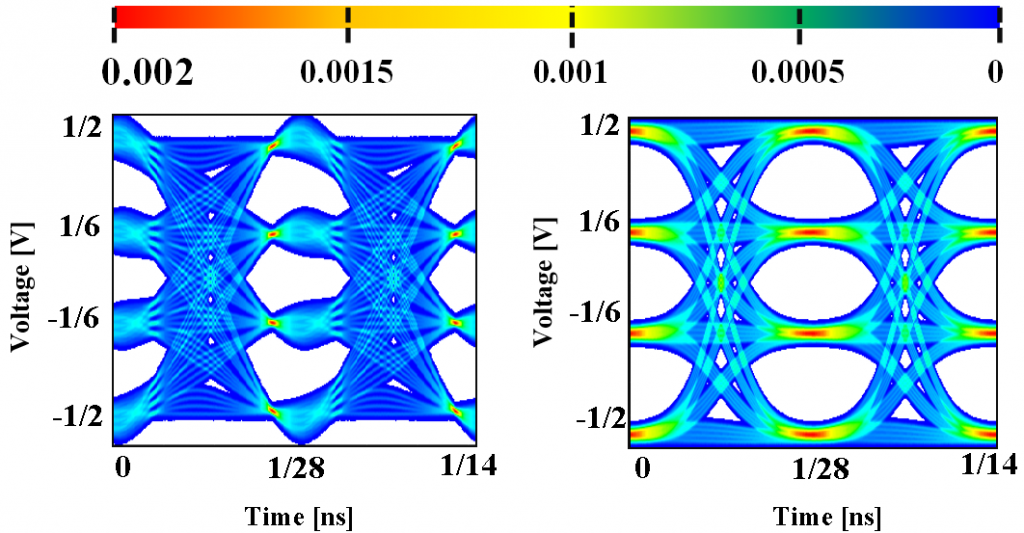

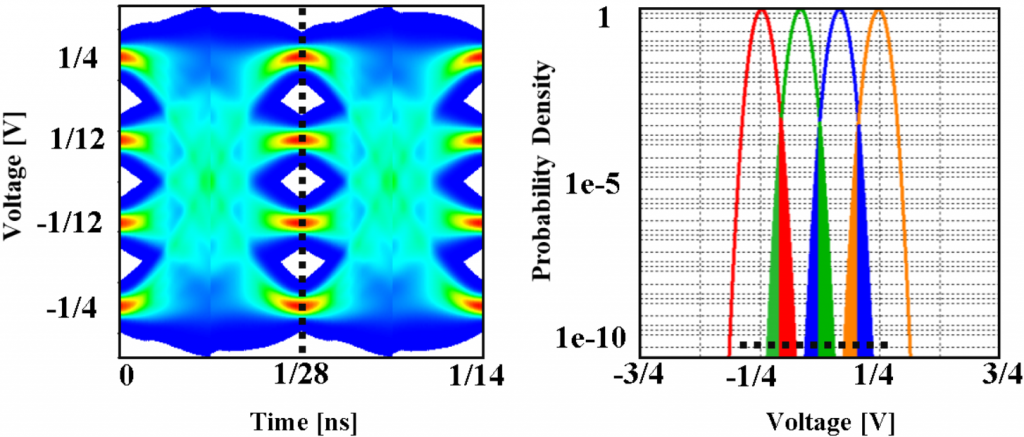

为 circuit 和 tran-co 工作流程生成统计眼图。可以观察到,将宏模型合成为集总元件的电路工作流程的眼图发生了变形,如下左图所示。右下图是 tran-co 工作流程的眼图。

图 5.电路 (a) 和 tran-co (b) 工作流程的统计眼图。

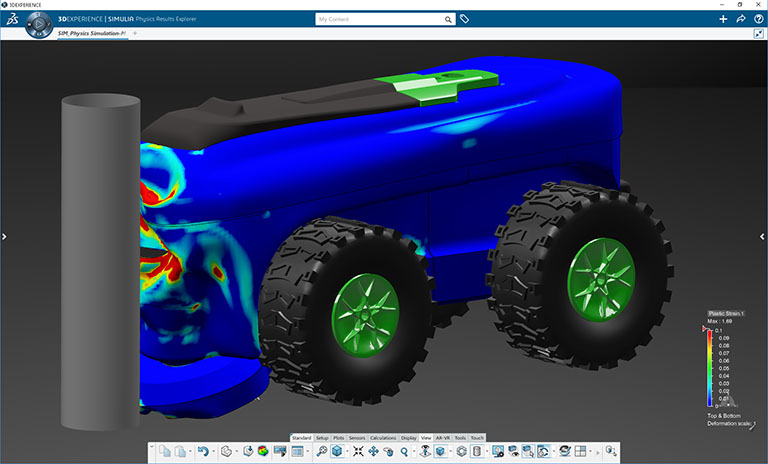

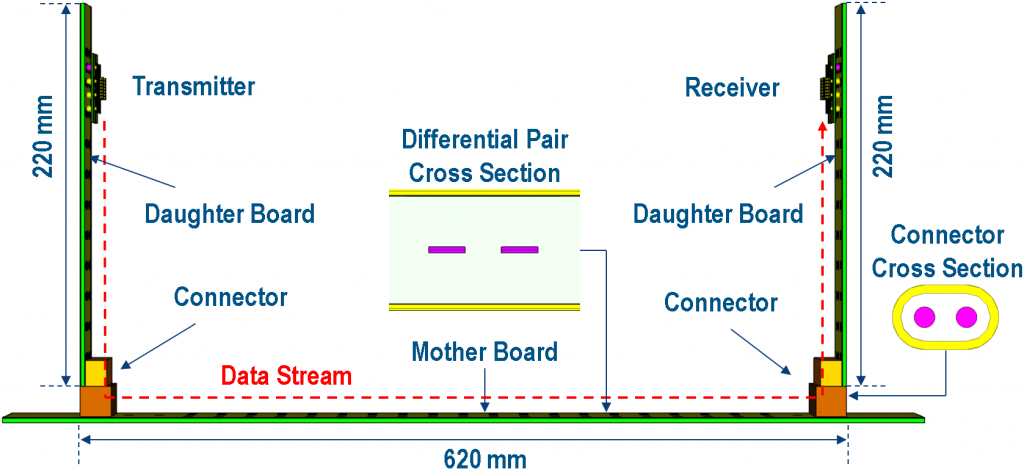

全 3D 背板通道仿真

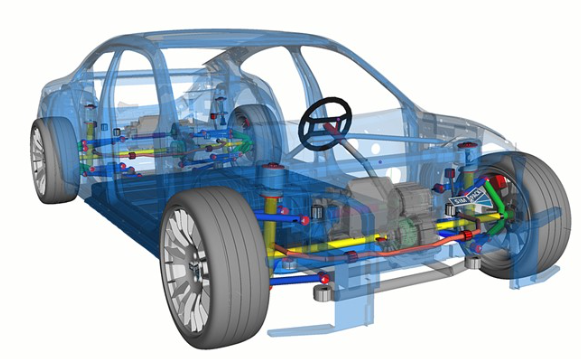

最后,我们按照 tran-co 工作流程在背板上模拟一个 1 米长的通道,如下图所示。传输线和连接器的差分阻抗优化到 100 欧姆。介电常数 = 3.2 的无损耗电介质用于基板。

图 6.背板上完整的 3D 无源通道。

获得阶跃响应后,使用具有 1 个前抽头和 2 个后抽头的 3 抽头 FFE(前馈均衡器)和 3 抽头 DFE(判决反馈均衡器)来改进统计眼图,其中不包括随机抖动。因此,每个级别的概率密度 (PD) 仅包含确定性抖动。我们将眼图的确定性抖动与随机噪声进行卷积,得到信噪比 (SNR) 为 12dB 的 PD,如下所示。

图 7.眼图虚线上的统计眼图和电压概率密度。

背板仿真工作流程概述

下图总结了用于 SerDes 仿真的 SIMULIA CST 解决方案。

图 8.SIMULIA CST SerDes 解决方案

CST Studio 套件具有 GPU 加速功能的时域求解器 [2] 可以有效地模拟 SerDes 通道中的电气大型无源互连。IBIS-AMI [1] 和 HSPICE [3] 仿真可以在 CST Design StudioTM 中运行。在 2022 版本中,组件库中将增加一个 IBIS-AMI 演示,以便用户可以顺利上手 IBIS-AMI 仿真。CST Studio Suite® IDEM [2] 提供了最先进的宏建模技术,可将 S 参数转换为 SPICE 模型。使用眼图工具,用户还可以将常见的 SerDes 技术(例如均衡或四级脉冲幅度调制 (PAM4))应用于他们的无源通道设计。眼图工具支持用户定义的随机抖动 (RJ) 和统计眼图。最后但并非最不重要的一点是,CST 和 Python 中的 VBA 宏编辑器可以轻松访问仿真结果(例如差分 S 参数或概率密度函数)。因此,用户可以使用 VBA 和 Python 脚本执行进一步分析,例如 IBIS-AMI 标准 [1] 不支持的通道工作裕量 (COM) [4]、误差传播 (EP) 和前向纠错 (FEC)。

获取正版软件免费试用资格,有任何疑问拨咨询热线:400-886-6353或 联系在线客服

未解决你的问题?请到「问答社区」反馈你遇到的问题,专业工程师为您解答!

- 相关内容

- 推荐产品